# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT (AN AUTONOMOUS INSTITUTION)

(Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **Department of Electronics & Communication**

# Engineering

# (2415521) Digital System Design with FPGAs Lab

M.TECH - I YEAR- I SEMESTER (ECE) R24 (MLRS) REGULATION

# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT

(AN AUTONOMOUS INSTITUTION)

(Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **INDEX**

| S. No | CONTENTS                                                                                                                                                 | Page No |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1     | CERTIFICATE                                                                                                                                              | i       |

| 2     | PREFACE                                                                                                                                                  | ii      |

| 3     | ACKNOWLEDGEMENT                                                                                                                                          | iii     |

| 4     | GENERAL INSTRUCTIONS                                                                                                                                     | iv      |

| 5     | SAFETY PRECAUTIONS                                                                                                                                       | v       |

| 6     | INSTITUTE VISION AND MISSION                                                                                                                             | vi      |

| 7     | DEPARTMENT VISION MISSION, PROGRAMME EDUCATIONAL OBJECTIVES                                                                                              | vii     |

| 8     | PROGRAMME OUTCOMES                                                                                                                                       | viii    |

| 9     | COURSE STRUCTURE, OBJECTIVES & OUTCOMES                                                                                                                  | x       |

| 10    | CO-PO MAPPING                                                                                                                                            | xi      |

| 11    | EXPERIMENTS                                                                                                                                              | xii     |

| 12    | HDL code to realize all the logic gates                                                                                                                  | 1-6     |

| 13    | Design and Simulation of Full Adder, Serial Binary Adder, Multi Precession Adder, Carry Look Ahead Adder.                                                | 7-13    |

| 14    | Design of Combinational circuit using Decoders.                                                                                                          | 14-16   |

| 15    | Design of Combinational circuit using encoder (without and with parity).                                                                                 | 17-22   |

| 16    | Design of Combinational circuit using multiplexer.                                                                                                       | 23-25   |

| 17    | Design of 4 bit binary to gray converter using MUX or Decoders.                                                                                          | 26-29   |

| 18    | Design of Multiplexer/ Demultiplexer, comparator in all 3 styles.                                                                                        | 30-35   |

| 19    | Modeling of an Edge triggered and Level triggered FFs: D, SR, and JK                                                                                     | 36-40   |

| 20    | Design of 4-bit binary, BCD counters (synchronous/ asynchronous reset) or any sequence counter                                                           | 41-45   |

| 21    | Design of a N- bit Register of Serial- in Serial –out, Serial in parallel out, Parallel in<br>Serial out and Parallel in Parallel Out using different FF | 46-48   |

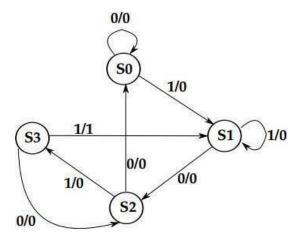

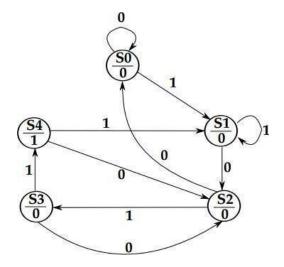

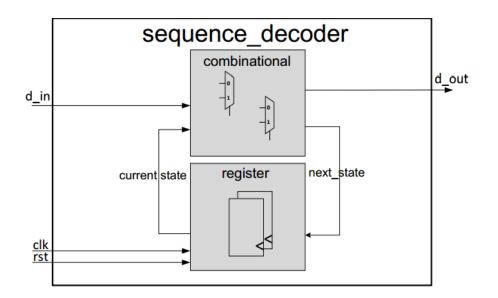

| 22 | Design of Sequence Detector (Finite State Machine- Mealy and Moore<br>Machines). |       |  |  |  |

|----|----------------------------------------------------------------------------------|-------|--|--|--|

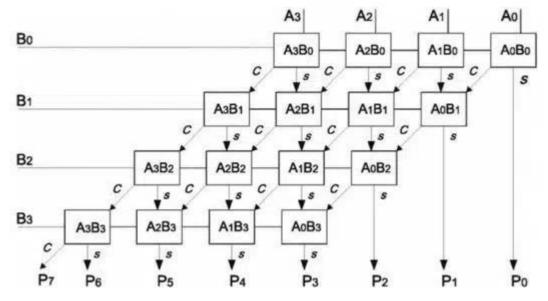

| 23 | Design of 4- Bit Multiplier, Divider.                                            | 53-54 |  |  |  |

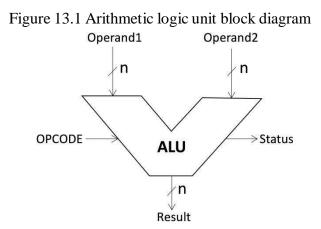

| 24 | Design of ALU to Perform – ADD, SUB, AND-OR, 1's and 2's Compliment              | 55-57 |  |  |  |

| 25 | Implementing the above designs on FPGA kits                                      | 58    |  |  |  |

MARRILAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT (AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **CERTIFICATE**

This is to certify that this manual is a bonafide record of practical work in the *Digital Systems Design with FPGAs lab* in I Semester of I -year M. Tech Sem I (ECE) Programme during the academic year 2022-2023. This book is prepared by Dr. N Srinivas (Associate Professor), Dr. K. Naveen Kumar (Associate Professor), Mrs. R Babitha (Assistant Professor), Mrs. B Manjula (Assistant Professor), Department of Electronics and Communication Engineering.

LAB I/C

Head of the Department

# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT

(AP AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act,1956

# **PREFACE**

It is one of the core areas of ECE and constitutes the largest applications in use today. Communication has entered into every part of today's world. This laboratory is intended to make students understand the use of different Digital Systems Design with FPGA's a n d is designed to help students understand the basic principles of design techniques as well as giving them the insight on design, simulation and hardware implementation of circuits. The main aim is to provide hands-on experience to the students so that they are able to put theoretical concepts to practice. The content of this course consists of two parts, 'simulation' and 'hardwired'. Students will carry out design experiments as a part of the experiments list provided in this lab manual. Students will be given a specific design problem, which after completion they will verify using the simulation software or hardwired implementation.

#### By,

Dr. N Srinivas (Associate Professor) Mrs. B Manjula (Assistant Professor) Mrs. R Babitha (Assistant Professor.

### MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT (AN AUTONOMOUS INSTITUTION)

(Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **ACKNOWLEDGEMENT**

It was really a good experience, working with *Digital Systems Design with FPGAs Laboratory*. First, we would like to thank Dr. N. Srinivas, Assoc. Professor, HOD of Department of Electronics and Communication Engineering, Marri Laxman Reddy Institute of technology & Management for his concern and giving the technical support in preparing the document.

We are deeply indebted and gratefully acknowledge the constant support and valuable patronage of Dr. Ravi Prasad, Dean, Marri Laxman Reddy Institute of technology & Management for giving us this wonderful opportunity for preparing the *Digital Communications Laboratory* manual.

We express our hearty thanks to Dr. R.Murali prasad, Principal, Marri Laxman Reddy Institute of technology & Management, for timely corrections and scholarly guidance.

At last, but not the least I would like to thanks the entire ECE Department faculty those who had inspired and helped us to achieve our goal.

By,

Dr.NSrinivas(Associate Professor) Mrs.B .Manjula (Assistant Professor) Mrs.R.Babitha (Assistant Professor)

# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT

(AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act,1956

# **GENERAL INSTRUCTIONS**

1. Students should report to the concerned labs as per the timetable schedule.

2. Students who turn up late to the labs will in no case be permitted to perform the experiment scheduled for the day.

3. After completion of the experiment, certification of the concerned staff in-charge in the observation book is necessary.

4. Students should bring a notebook of about 100 pages and should enter the readings/observations into the notebook while performing the experiment.

5. The record of observations along with the detailed experimental procedure of the experiment.

6. Performed in the immediate last session should be submitted and certified by the staff member in-charge.

7.. Not more than one student is permitted to perform the experiment on a setup.

8. When the experiment is completed, students should disconnect the setup made by them, and should return all the components/instruments taken for the purpose.

9. Any damage of the equipment or burnout of components will be viewed seriously by putting penalty.

10. Students should be present in the labs for the total scheduled duration.

11. Students are required to prepare thoroughly to perform the experiment before coming to Laboratory.

12. Procedure sheets/data sheets provided to the student's should be maintained neatly and to be returned after the experiment.

MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT (AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **SAFETY PRECAUTIONS**

1. No horseplay or running is allowed in the labs.

2. No bare feet or open sandals are permitted.

3. Before energizing any equipment, check whether anyone is in a position to be injured by your actions.

4. Read the appropriate equipment instruction manual sections or consult with your instructor.

5. Before applying power or connecting unfamiliar equipment or instruments into any circuits.

6. Position all equipment on benches in a safe and stable manner.

7. Do not make circuit connections by hand while circuits are energized. This is especially.

8. Dangerous with high voltage and current circuits.

MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT (AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# **INSTITUTION VISION AND MISSION**

### VISION

To establish as an ideal academic institution in the service of the nation, the world and the humanity by graduating talented engineers to be ethically strong, globally competent by conducting high quality research, developing breakthrough technologies, and disseminating and preserving technical knowledge.

### MISSION

To fulfill the promised vision through the following strategic characteristics and aspirations:

- A. Contemporary and rigorous educational experiences that develop the engineers and managers;

- B. An atmosphere that facilitates personal commitment to the educational success of students in an environment that values diversity and community;

- C. Prudent and accountable resource management;

- D. Undergraduate programs that integrate global awareness, communication skills and team building;

- E. Leadership and service to meet society's needs;

- F. Education and research partnerships with colleges, universities, and industries to graduate education and training that prepares students for interdisciplinary engineering research and advanced problem-solving abilities;

- G. Highly successful alumni who contribute to the profession in the global society.

# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT

(AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

# DEPARTMENT VISION, MISSION, PROGRAMME EDUCATIONAL OBJECTIVES AND SPECIFIC OUTCOMES

# Vision and Mission

#### **Our Vision**

Imparting quality technical education through research, innovation and team work for a lasting technology development in the area of Electronics and Communication Engineering.

#### **Our Mission**

To develop a strong center of excellence for education and research with excellent infrastructure and well qualified faculties to instill in them a passion for knowledge.

#### To achieve the Mission the department will:

- M1: Establish a unique learning environment to enable the students to face the challenges of the Electronics and Communication Engineering field.

- M2: Promote the establishment of center of excellence in niche technology areas to nurture the spirit of innovation and creativity among faculty and students.

- M3: Provide ethical and value-based education by promoting activities addressing the societal needs.

- M4: Enable students to develop skills to solve complex technological problems of current times and also provide a framework for promoting collaborative and multidisciplinary activities.

#### PEO's & PO's

#### **PROGRAMME EDUCATIONAL OBJECTIVES**

PEO 1: Have successful careers in Industry.

PEO 2: Show excellence in higher studies/ Research.

#### Program Outcomes (PO)

- **PO 1:** Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and engg. specialization to the solution of complex engineering problems.

- **PO 2:** Problem analysis: Identify, formulate, research literature, and analyze engineering problems to arrive at substantiated conclusions using first principles of mathematics, natural, and engineering sciences.

- **PO 3:** Design/development of solutions: Design solutions for complex engineering problems and design system components, processes to meet the specifications with consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- **PO 4:** Conduct investigations of complex problems: Use research-based knowledge including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- **PO 5:** Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- **PO 6:** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal, and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- **PO 7:** Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **PO 8:** Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **PO 9:** Individual and team work: Function effectively as an individual, and as a member or leaderinteams,andinmultidisciplinarysettings.

- **PO 10:** Communication: Communicate effectively with the engineering community and with society at large. Be able to comprehend and write effective reports documentation. Make effective presentations, and give and receive clear instructions.

- **PO** 11: Project management and finance: Demonstrate knowledge and understanding of engineering and management principles and apply these to one's own work, as a member and leader in a team. Manage projects in multidisciplinary environments.

- **PO 12:** Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

#### COURSE STRUCTURE

| Level | Credits | Periods/Week | Prerequisites         |

|-------|---------|--------------|-----------------------|

|       |         |              | Entire subject of     |

| PG    | 2       | 3            | Digital System Design |

#### **Evaluation Scheme:**

| MID (Internal Lab) Semester Test      | 40 marks |

|---------------------------------------|----------|

| End Semester Lab external Examination | 60marks  |

The end semester examination shall be conducted with an external examiner and internal examiner.

The external examiner shall be appointed by the principal / Chief Controller of examinations

#### **Course Objectives:**

- The ability to code and simulate any digital function in Verilog HDL.

- Know the difference between synthesizable and non-synthesizable code.

- Understand library modeling, behavioral code and the differences between them.

- Understand the differences between simulator algorithms.

- Learn good coding techniques per current industrial practices.

- Understand logic verification using Verilog simulation.

#### **Course Outcomes:**

#### At the end of the laboratory work, students will be able to

- Describe Verilog hardware description languages (HDL).

- Design Digital Circuits in Verilog HDL.

- Write behavioral models of digital circuits.

- Write Register Transfer Level (RTL) models of digital circuits.

- Verify behavioral and RTL models.

- Describe standard cell libraries and FPGAs.

- Synthesize RTL models to standard cell libraries and FPGAs.

- Implement RTL models on FPGAs and Testing & Verification. Course Outcomes (COs)

At the end of the laboratory work, students will be able to

**CO1:** To Design Digital Circuits in Verilog HDL.

CO2: Write behavioral models of digital circuits.

**CO3:** Verify behavioral and RTL models.

**CO4:** To Synthesize RTL models to standard cell libraries and FPGAs.

CO5: To Implement RTL models on FPGAs and Testing & Verification.

Course Outcomes (CO's)–Program Outcomes (PO's)Mapping

| CO's <sub>Po's</sub> | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | <b>PO7</b> | PO8 | PO9 | PO10 | PO11 | PO12 |

|----------------------|-----|-----|-----|-----|-----|-----|------------|-----|-----|------|------|------|

| CO1                  | 3   | 3   | -   | -   | 3   | -   | -          | -   | -   | -    | -    | -    |

| CO2                  | 3   | 3   | -   | -   | 3   | -   | -          | -   | -   | -    | -    | -    |

| CO3                  | 3   | 3   | -   | -   | 3   | -   | -          | -   | -   | -    | -    | -    |

| CO4                  | 3   | 3   | -   | -   | 3   | -   | -          | -   | -   | -    | -    | -    |

| CO5                  | 3   | 3   | _   | -   | 3   | -   | -          | -   | -   | -    | -    | -    |

• Simple-1

Moderate-2

High-3

# MARRI LAXMAN REDDY INSTITUTE OF TECHNOLOGY AND MANAGEMENT

(AN AUTONOMOUS INSTITUTION) (Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad) Accredited by NBA and NAAC with 'A' Grade & Recognized Under Section2(f) & 12(B)of the UGC act, 1956

#### 2215521: DIGITAL SYSTEM DESIGN WITH FPGAs LAB (Lab - I)

I Year M.Tech (ES) I - Sem.

L T P C 0 0 3 2

Programming can be done using any complier. Down load the programs on FPGA/CPLD boards and performance testing may be done using pattern generator (32 channels) and logic analyzer apart from verification by simulation with any of the front-end tools.

- 1. HDL code to realize all the logic gates

- 2. Design and Simulation of Full Adder, Serial Binary Adder, Multi Precession Adder, CarryLook Ahead Adder.

- 3. Design of Combinational circuit using Decoders.

- 4. Design of Combinational circuit using encoder (without and with parity).

- 5. Design of Combinational circuit using multiplexer.

- 6. Design of 4 bit binary to gray converter using MUX or Decoders.

- 7. Design of Multiplexer/ Demultiplexer, comparator in all 3 styles.

- 8. Modelling of an Edge triggered and Level triggered FFs : D, SR, JK

- Design of 4-bit binary, BCD counters (synchronous/ asynchronous reset) or any sequencecounter

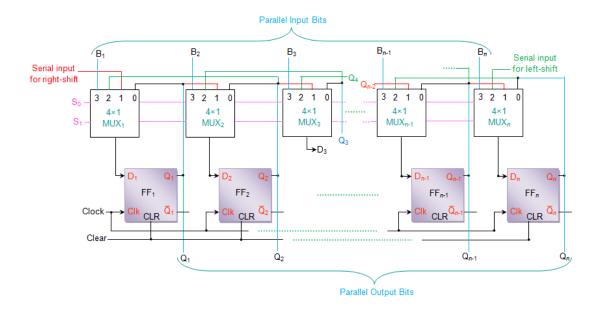

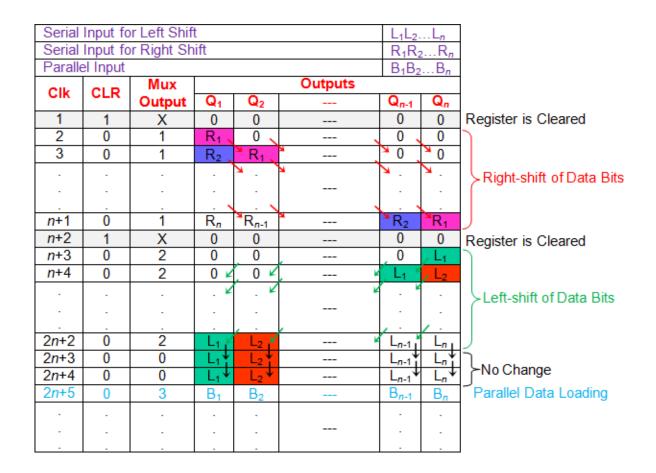

- Design of a N- bit Register of Serial- in Serial -out, Serial in parallel out, Parallel in Serial out and Parallel in Parallel Out using different FFs.

- 11. Design of Sequence Detector (Finite State Machine- Mealy and Moore Machines).

- 12. Design of 4- Bit Multiplier, Divider.

- 13. Design of ALU to Perform ADD, SUB, AND-OR, 1's and 2's Compliment,

- 14. Implementing the above designs on FPGA kits.

# HDL CODE TO REALIZE ALL

# LOGIC GATES

EXPT. NO: 1

DATE:

AIM: To develop the source code for logic gates by using VERILOG and obtain thesimulation,

Synthesis, place and route and implement into FPGA.

# SOFTWARE & HARDWARE:

- 1. CADENCE

- 2. FPGA-SPARTAN-3

LOGIC DIAGRAM:

# AND GATE:

# LOGIC DIAGRAM:

| Α | B | Y=AB |

|---|---|------|

| 0 | 0 | 0    |

| 0 | 1 | 0    |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

## OR GATE

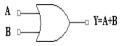

LOGIC DIAGRAM

A

B

Y=A+B

0

0

0

0

1

1

1

0

1

1

1

1

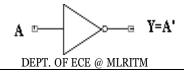

# NOT GATE:

## LOGIC DIAGRAM:

#### **TRUTH TABLE:**

| Α | Y=A' |

|---|------|

| 0 | 0    |

| 1 | 0    |

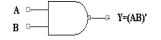

# NAND GATE:

# LOGIC DIAGRAM:

| Α | B | Y=(AB)' |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

#### **TRUTH TABLE:**

#### OR GATE

LOGIC DIAGRAM

| Α | B | Y=A+B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

#### TRUTH TABLE

#### XOR GATE

### LOGIC DIAGRAM

#### **TRUTH TABLE:**

| Α | B | Y=A⊕B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 0     |

#### **XNOR GATE:**

#### LOGIC DIAGRAM:

| ſ | Α | B | Y=A⊕B |

|---|---|---|-------|

| ľ | 0 | 0 | 1     |

|   | 0 | 1 | 0     |

|   | 1 | 0 | 0     |

| Ī | 1 | 1 | 1     |

#### **TRUTH TABLE:**

#### **Description:**

A logic gate is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logical inputs, and produces a single logical output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and unlimited fan-out, or it may refer to a non-ideal physical device.

## **VERILOG SOURCE CODE:**

#### **DATA FLOW MODEL:**

```

modulelogicgates1(a,b,c); input a;

input b; output [6:0]c;

assignc[0]=a&b;

assignc[1]=a|b;

assignc[2]=~(a&b);

assign c[3]=~(a|b);

assignc[4]=a^ b;

assignc[5]= ~(a^ b);

assign c[6]=~ a;

endmodule

(OR)

module all(a,b,an,o,na,no,nt,xo,xn);

input a,b;

DEPT. OF ECE @ MLRITM

```

```

output (an,na,no,nt,xo,xn);

```

```

assign#5 an=a&b;

```

assign#5 na=~(a&b);

assign#5 o=a|b;

```

assign#5 no=~(a|b);

```

assign#5 nt=~a;

assign#5 xo=a^b;

assign#5 xn=~(a^b);

endmodule

## **BEHAVIOURAL MODELLING OF AND GATE:**

module andg(a,b,an); input a,b;

output an; reg an;

always @(a or b) begin

if(a==1`b0 && b==1`b0) an=1`b0;

else if(a==1`b0 && b==1`b1) an=1`b0;

else if(a==1`b1 && b=1`b0) an=1`b0;

else if(a==1`b1 && b==1`b1) an=1`b1;

end

endmodule

# BEHAVIOURAL MODEL FOR OR GATE,NOR,NAND,NOR,XOR,X-NOR:

module all(a,b,o,na,no,nt,xo,xn);

input a,b;

output(o,na,,o,nt,xo,xn);

reg o,na,no,nt,xo,xn;

always @(a or b)

begin

o=a|b;

na = (a|b);

nt=~(a);

xo=(a^b);

xn=~(a^b);

endmodule

## STRUCTURAL MODEL:

DEPT. OF ECE @ MLRITM

module all(a,b,an,o,na,no,nt,xo,xn);

input a,b;

output (an,o,na,no,nt,xo,xn);

wire t1,t2,t3,t4;

and a1,(an,a,b);

or a2(o,a,b);

not a3(nt,a);

and a4(t1,a,b);

not a5(na,t1);

or a6(t2,a,b);

not a7(no,t2);

xor a8(xo,a,b);

xor a9(t3,a,b);

not a10(xn,t3);

endmodule

#### MIXED MODEL:

module all(a,b,an,o,na,no,nt,xo,xn);

input a,b;

output (an,o,na,no,nt,xo,xn);

reg na,no,nt,xo,xn;

assign #5 an=a&b;

assign #5 o=a|b: not a1(nt,a);

always @(a or b)

begin na=~(a&b);

no=~(a^b); xo=a^b;

xn=~(a^b);

end

endmodule

#### Simulation output:

DEPT. OF ECE @ MLRITM

|       | /logicgates/a<br>/logicgates/b<br>/logicgates/c<br>- (6)<br>- (5)<br>- (4)<br>- (3)<br>- (2)<br>- (1)<br>- (0) | 1<br>0100011<br>0<br>1<br>0<br>0<br>0<br>1<br>1<br>1 | 1101100 | <u>(0010110</u> |  |

|-------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------|-----------------|--|

| Gates | А                                                                                                              |                                                      | В       | Y               |  |

| NOT   | 0                                                                                                              |                                                      | X       |                 |  |

|       | 1                                                                                                              |                                                      | X       |                 |  |

| AND   | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

| OR    | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

| NAND  | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

| NOR   | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

| XOR   | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

| XNOR  | 0                                                                                                              |                                                      | 0       |                 |  |

|       | 0                                                                                                              |                                                      | 1       |                 |  |

|       | 1                                                                                                              |                                                      | 0       |                 |  |

|       | 1                                                                                                              |                                                      | 1       |                 |  |

EXPT. NO: 2

#### Adder, Carry Look Ahead Adder

DATE:

**AIM:**To write a HDL code to describe the functions of a full Adder Serial Binary Adder, Multi Precession Adder, Carry Look Ahead Adder.

#### **RESOURCES**

PC installed with CADENCE tool

### PROGRAM LOGIC

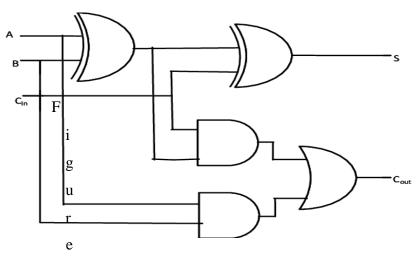

A full adder consists of 3 inputs and 2 outputs. Fig 7.1 shows truth table of full adder. Use "assign" keyword to represent design in data flow style. The output signal expressions can be obtained from the truth table using K-maps.

2.1 Logic diagram for 1-bit full adder

| I | Inputs |     | Out | able 2.1 |                                               |

|---|--------|-----|-----|----------|-----------------------------------------------|

|   | В      | Cin | Sum | Carry    | uoie 2.1                                      |

|   | 0      | 0   | 0   | 0        | Truth                                         |

|   | 0      | 1   | 1   | 0        | 4 - <b>1</b> - <b>1</b> - <b>1</b> - <b>1</b> |

|   | 1      | 0   | 1   | 0        | table for                                     |

|   | 1      | 1   | 0   | 1        | 1-bit                                         |

|   | 0      | 0   | 1   | 0        |                                               |

|   | 0      | 1   | 0   | 1        | full                                          |

|   | 1      | 0   | 0   | 1        | adder                                         |

|   | 1      | 1   | 1   | 1        | audel                                         |

DEPT. OF ECE @ MLRITM

Т

### **PROCEDURE**

- Create a module with required number of variables and mention it's input/output.

- Write the description of the full adder in 3 styles.

- Create another module referred as test bench to verify the functionality.

- Follow the steps required to simulate the design and compare the obtained output with the required one.

# <u>CODE</u>

// full adder

module p10(a,b,c,sum,carry); output sum,carry; input a,b,c; wire y0,y1,y2; xor g1(y0,a,b); and g2(y1,a,b); xor g3(sum,y0,c); and g4(y2,y0,c); or g5(carry,y2,y1); endmodule

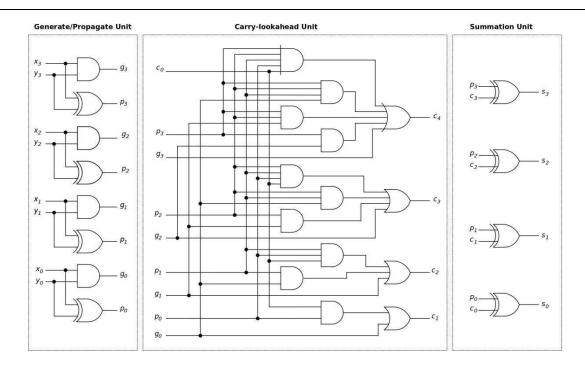

To design and simulate the HDL code for carry look ahead adder

#### **PROGRAM LOGIC**

Ripple-carry addition suffers from an impractical propagation delay cause by the

sequential generation of arithmetic carries. In other words,  $c_{i+1}$  is dependent on  $c_i$ , which is further dependent on  $c_{i-1}$ , etc. The effect of this carry chain is a propagation delay that has a linear dependency on n, the bit width of the adder. Therefore, methods that compute the arithmetic carries in parallel have potential performance benefits over ripple-carry addition.

As the name implies, carry-look ahead is one such technique for high-speed addition that computes arithmetic carries in a parallel fashion. To understand how exactly a carry-look ahead adder works, consider the addition of two numbers, *X* and *Y*, such that  $x_{i}$  is the  $i^{th}$  ith binary digit of *X*, and *y* is  $t_{i}$  he *ith* binary digit

of Y. The (i+1)th arithmetic carry is  $c_{i+1}$  and is computed as follows:

$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$  (1)

$= x_i y_i + (x_i + y_i)c_i \tag{2}$

The effect of simply factoring out ci from the last two terms in expression (1) is shown in expression (2). Now observe that  $c_{i+1}$  is logic '1' if either of the two conditions exists:

x<sub>i</sub>y<sub>i</sub> is logic

'1'

$x_i + y_i$  is logic '1'1 and there is a previous carry (i.e.  $c_i=1$ )

Therefore,  $x_i y_i$  is referred to as generate function because when '1', a carry is generated, while  $x_i + y_i$  is referred to as the propagate function because when '1', it will propagate a carry. In mathematical terms, we see that

$g_i = x_i y_i$ (3)  $p_i = x_i + y_i$ (4)  $c_{i+1} = g_i + p_i c_i$ (5)

Clearly, expressions (3) and (4) do not depend on the carry in the previous bit position and thus, can be generated in parallel. It turns out, we can write expression (5) for the first four carries in such a way that they, too, do not depend on one another, but rather only depend on the input carry, c0, and the gi and pi. Examine the expressions below to convince yourself of this.

$$c_{1} = g_{0} + p_{0}c_{0}$$

$$c_{2} = g_{1} + p_{1}c_{1} = g_{1} + p_{1}g_{0} + p_{1}p_{0}c_{0}$$

$$c_{3} = g_{2} + p_{2}c_{2} = g_{2} + p_{2}g_{1} + p_{2}p_{1}g_{0} + p_{2}p_{1}p_{0}c_{0}$$

$$c_{4} = g_{3} + p_{3}c_{3} = g_{3} + p_{3}g_{2} + p_{3}p_{2}g_{1} + p_{3}p_{2}p_{1}g_{0} + p_{3}p_{2}p_{1}p_{0}c_{0}$$

Although the expression for <sup>ci</sup> becomes increasingly complex, the theoretical gate-

delay for each of the above expressions, given the gi 's, pi 's, and c0 , is  $\Delta g =$

2. However, the increased complexity is reflected in the number of inputs to each gate (i.e. the gate fan-in) and the number of gates required. Figure 1 illustrates this point with the gate-level schematic for each of the sub-modules within a 4-bit carry-lookahead adder. One thing to note is that:

$p_i = x_i \oplus y_i$

$s_i = p_i \oplus c_i$

In other words, expression (10) is being used in lieu expression (4). It turns out that expression (5) works correctly in either case, and the former allows the Sum to be computed with expression (11). Before moving on, let us try to understand how data flows through the 4-bit carry-lookahead adder. To do so, we enumerate through the steps below:

Data arrives at the Generate/Propagate Unit, and the  $g_i$ 's and  $p_i$ 's, are computed in one gate-delay (i.e. $\Delta g= 1$ ).

The gi 's and pi 's are forwarded to the Carry-Lookahead Unit, which generates all of the carries in two gate-delays,  $\Delta g = 2$ .

The carries are then fed into the Summation Unit, which computes the sum bits, the  $S_i$ 's, in one gate-delay  $\Delta g = 1$ .

Figure 2.2 Carry-look ahead Adder

For simplicity, we are assuming that all gates have the same delay time. This assumption may or may not be true depending on the target technology that is being used to implement your logic. However, for the sake of comparison with other addition techniques, this model works well. Summarizing the above steps, we can see that the propagation delay for a 4-bit adder is no longer determined by a carry chain and is only four gate-delays, ( $\Delta g$ = 4). The pre-lab assignment will include an exercise which asks you to look at the gate count of a 4-bit Carry- Look ahead Adder.

#### **PROCEDURE**

Create a module with required number of variables and mention it's

input/output.

Write the description of the carry look ahead adder using data flow model or gate level model.

Create another module referred as test bench to verify the functionality.

Follow the steps required to simulate the design and compare the obtained output with the required one.

#### CODE

module p21(a,b,cin,sum,cout);

input[3:0] a,b;

```

input cin;

output [3:0] sum; output cout;

wire p0,p1,p2,p3,g0,g1,g2,g3,c1,c2,c3,c4;

assign p0=(a[0]^{b}[0]),

p1=(a[1]^b[1]),

p2=(a[2]^b[2]),

p3=(a[3]^b[3]);

assign g0 = (a[0]\&b[0]),

g1=(a[1]&b[1]),

g2=(a[2]&b[2]),

g3=(a[3]&b[3]);

assign c0=cin, c1=g0|(p0\&cin),

c2=g1|(p1&g0)|(p1&p0&cin),

c3=g2|(p2&g1)|(p2&p1&g0)|(p1&p1&p0&cin),

c4=g3|(p3&g2)|(p3&p2&g1)|(p3&p2&p1&g0)|(p3&p2&p1&p0&cin); assign

sum[0] = p0^{c0},

sum[1]=p1^c1,

sum[2]=p2^c2,

sum[3]=p3^c3;

```

assign cout=c4;

endmodule

#### PRE LAB QUESTIONS

- 1. What is the functionality of the adder?

- 2. Design a ripple carry adder and mention its disadvantage.

- 3. List the various adders and its pros and cons.

- 4. What is a half adder?

- 5. Write the sum and carry expression for half adder.

- 6. What is a full adder?

- 7. Write the sum and carry expression for 1-bit full adder.

- 8. Write the difference and barrow out expressions for 1-bit subtractor

- 9. What is a parallel adder/subtractor?

# LAB ASSIGNMENT

- 1. Design 4-bit ripple carry adder using HDL.

- 2. Design 4-bit carry look ahead adder using HDL.

- 3. Observe the RTL schematic of the designed 4-bit look ahead adder.

- 4. Design a 4-bit ripple carry adder using full adders.

- 5. Implement full adder using decoder.

- 6. Implement full subtractor using decoder.

- 7. Implement a 4-bit adder/subtractor.

- 8. Design a full adder using minimum number of NAND gates.

#### POST LAB QUESTIONS

1 Realize a full adder using two half adders.

2 What is the amount of delay involved in ripple carry adder?

3 Compare serial adder and parallel adder with respect to speed and complexity.

4 Implement a single circuit which can perform both addition and subtraction operations on binary input bits.

EXPT. NO: 3

DATE:

#### AIM:

To design and simulate the HDL code for the following combinational circuits

3 to 8 Decoder

RESOURCES

PC installed with CADENCE tool

#### PROGRAM LOGIC

#### Program logic for Decoder

A decoder is a multiple-input, multiple-output logic circuit which converts coded inputs into coded outputs, where the input and output codes are different. The input code generally has fewer bits than the output code. Each input code word produces a different output code word, i.e., there is one-to-one mapping from input code words into output code words. This one-to-one mapping can be expressed in a truth table.

The most common decoder circuit is an n-to- $2^n$  decoder or binary decoder. Such a decoder has an n-bit binary input code and a 1-out-of- $2^n$  output code. A binary decoder is used when you need to activate exactly one of  $2^n$  outputs based on an n- bit input value.

Figure 3.1 shows the general structure of the 3 to 8 decoder circuit and its truth table.

|            | → y <sub>0</sub> = a'b'c'            | a b c | : <b>y</b> <sub>0</sub> | <i>y</i> <sub>1</sub> | <i>y</i> <sub>2</sub> | <i>Y</i> <sub>3</sub> | <i>Y</i> <sub>4</sub> | <i>Y</i> <sub>5</sub> | <i>Y</i> <sub>6</sub> | <i>Y</i> <sub>7</sub> |

|------------|--------------------------------------|-------|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|            | → y <sub>1</sub> = a'b'c             | 000   | ) 1                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

|            | → y <sub>2</sub> = a'bc'             | 001   | 0                       | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| a → 3-to-8 | $\rightarrow$ y <sub>3</sub> = a'bc  | 010   | 0 0                     | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| b→ line    |                                      | 011   | 0                       | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     | 0                     |

| decoder    | $\rightarrow$ y <sub>4</sub> = ab'c' | 100   | 0 0                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     | 0                     |

| · - [      | → y <sub>5</sub> = ab'c              | 101   | 0                       | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     |

|            | → y <sub>6</sub> = abc'              | 110   | 0 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     | 0                     |

|            | $\rightarrow$ y <sub>7</sub> = abc   | 111   | 0                       | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     |

Figure 3.1: General Structure of 3 to 8 Decoder and its truth table

#### CODE:

$/\!/$  3 to 8 decoder

module p3(i,d);input [2:0]i; output [7:0]d; assign d[0]=(~i[2])&(~i[1])&(~i[0]); assign d[1]=(~i[2])&(~i[1])&(i[0]); assign d[2]=(~i[2])&(i[1])&(i[0]); assign d[3]=(~i[2])&(i[1])&(i[0]); assign d[5]=(i[2])&(~i[1])&(~i[0]); assign d[6]=(i[2])&(i[1])&(~i[0]); assign d[7]=(i[2])&(i[1])&(i[0]);endmodule

## PRE LAB QUESTIONS

1 What is a decoder?

2 What for enable inputs are used in decoder?

#### LAB ASSIGNMENT

- 1. Implement full adder circuit using decoder and two OR gates.

- 2. Implement 3x8 decoder using 2x4 decoder and additional logic.

- 3. Construct a 4x16 decoder using two 3x8 decoder and additional logic. Show the schematic diagram neatly?

- 4. Design 2-to-4 decoder using only NOR gates.

- 5. Construct a 5 x 32 decoder with four 3x 8 decoders with enable and one 2 x 4 decoder.

Design of Combinational circuit using encoder (without and with parity).

EXPT. NO: 4

DATE:

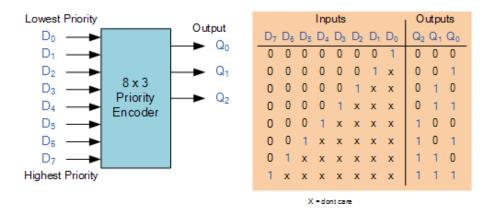

**AIM:** To design and simulate the HDL code for the following combinational circuits 8 to 3 Encoder (With priority and without priority).

#### <u>RESOURCES</u>

PC installed with CADENCE tool.

#### Program logic for Encoder

An encoder has M input and N output lines. Out of M input lines only one is activated at a time and produces equivalent code on output N lines. If a device output code has fewer bits than the input code has, the device is usually called an encoder. Example Octal-to-Binary take 8 inputs and provides 3 outputs. For an 8- to-3 binary encoder with inputs D0-D7 the logic expressions of the outputs XYZ are obtained by using the Table 4.1.

> X = D4 + D5 + D6 + D7 Y = D2 + D3 + D6 + D7Z = D1 + D3 + D5 + D7

> > a b l e

4

Т

|                       | 1            |

|-----------------------|--------------|

|                       | :            |

|                       |              |

|                       | Т            |

|                       | r            |

|                       | u            |

|                       | t            |

|                       | h            |

|                       |              |

|                       | Т            |

|                       | а            |

|                       | b            |

|                       | 1            |

|                       | e            |

|                       |              |

|                       | f            |

|                       | 0            |

|                       | r            |

|                       |              |

|                       | 8            |

|                       | -            |

|                       | 3            |

|                       |              |

|                       | Е            |

|                       | n            |

|                       | c            |

|                       | 0            |

|                       | d            |

|                       | e            |

|                       | r            |

|                       |              |

|                       | W            |

| DEPT. OF ECE @ MLRITM | i<br>Page 18 |

- t h

- D

- 7

- -

- D

- 0

- i

- n

- р

- u

- .

- t

|                       |                |    |                       |                |                |                |    |                | S  |                |  |

|-----------------------|----------------|----|-----------------------|----------------|----------------|----------------|----|----------------|----|----------------|--|

|                       | INPUTS         |    |                       |                |                |                |    | OUTPUTS        |    |                |  |

| <b>Y</b> <sub>7</sub> | Y <sub>6</sub> | Y₅ | <b>Y</b> <sub>4</sub> | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Yo | A <sub>2</sub> | A1 | A <sub>0</sub> |  |

| 0                     | 0              | 0  | 0                     | 0              | 0              | 0              | 1  | 0              | 0  | 0              |  |

| 0                     | 00             | 0  | 0                     | 0              | 0              | 1              | 0  | 0              | 0  | 1              |  |

| 0                     | n <sup>0</sup> | 0  | 0                     | 0              | 1              | 0              | 0  | 0              | 1  | 0              |  |

| 0                     | e <sup>0</sup> | 0  | 0                     | 1              | 0              | 0              | 0  | 0              | 1  | 1              |  |

| 0                     | 0              | 0  | 1                     | 0              | 0              | 0              | 0  | 1              | 0  | 0              |  |

| 0                     | o <sup>0</sup> | 1  | 0                     | 0              | 0              | 0              | 0  | 1              | 0  | 1              |  |

| 0                     | f 1            | 0  | 0                     | 0              | 0              | 0              | 0  | 1              | 1  | 0              |  |

| 1                     | 0              | 0  | 0                     | 0              | 0              | 0              | 0  | 1              | 1  | 1              |  |

t

he main disadvantages of standard digital encoders is that they can generate the wrong output code when there is more than one input present at logic level "1".

The Priority Encoder solves the problems mentioned above by allocating a priority level to each input. The priority encoders output corresponds to the currently active input which has the highest priority. So when an input with a higher priority is present, all other inputs with a lower priority will be ignored. The priority encoder comes in many different forms with an example of an 8- input priority encoder along with its DEPT. OF ECE @ MLRITM Page 19

#### truth table shown in Figure 4.1

#### <u>PROCEDURE</u>

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Implement the logic for decoder or encoder using behavioral or gate level model.

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

## <u>CODE</u>

// 8 to 3 Encoder without priority module

p2(d,e);

input [7:0] d;

output [2:0]e;

assign e[2]= d[4] | d[5] | d[6] | d[7];

assign e[1]= d[2] | d[3] | d[6] | d[7];

assign e[0]= d[1] | d[3] | d[5] | d[7];

endmodule

// 8 to 3 Encoder with priority module

p4(din, dout);

input [7:0] din;

output [2:0] dout;

reg [2:0] dout;

DEPT. OF ECE @ MLRITM

Page 20

```

always

(din)

begin

if (din[7]==1'b1) dout=3'b111;

else if (din[6]==1'b1) dout=3'b110; else

if (din[5]==1'b1) dout=3'b101; else if

(din[4]==1'b1) dout=3'b100;

else if

(din[3]==1'b1) dout=3'b011;

else if

(din[2]==1'b1) dout=3'b010;

else if

(din[1]==1'b1) dout=3'b001;

else if

dout=3'b000;

(din[0] == 1'b1)

else

dout=3'bXXX;

end

endmodule

```

### PRE LAB QUESTIONS

- 1. What is an encoder?

- 2. What is a priority encoder?

- 3. How many input and output lines are there for a 128x7 encoder.

#### LAB ASSIGNMENT

- 1. Write a Verilog code to implement Octal-to-Binary Encoder?

- 2. Write a Verilog code to implement a 8x3 Priority Encoder?

- 3. Write a Verilog code to implement Decimal-to-BCD Encoder?

#### POST LAB QUESTIONS

- 1. Write code for a parallel encoder and a priority encoder.

- 2. What is the difference between wire and reg data type ?

- 3. What is the difference between the following two lines of Verilog code? #5 a

- = b;

a = #5 b;

4. What is the use of Priority Encoder?

Design of Combinational circuit using multiplexer.

EXPT. NO: 5

AIM: To write HDL codes for an 8X1 multiplexer r and verify its functionality.

# <u>RESOURCES</u>

PC installed with CADENCE tool

# PROGRAM LOGIC

In the large-scale-digital systems, a single line is required to carry on two or more digital signals – and, of course! At a time, one signal can be placed on the one line. But, what is required is a device that will allow us to select; and, the signal we wish to place on a common line, such a circuit is referred to as multiplexer.

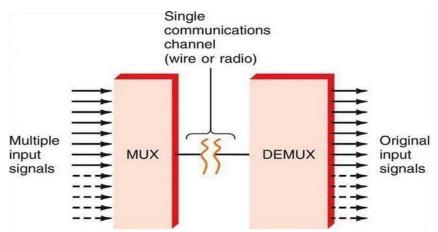

The function of a multiplexer is to select the input of any 'n' input lines and feed that to one output line. The function of a de-multiplexer is to inverse the function of the multiplexer and the shortcut forms of the multiplexer. The de-multiplexers are mux and demux. Some multiplexers perform both multiplexing and de-multiplexing operations. The main function of the multiplexer is that it combines input signals, allows data compression,

and shares a single transmission channel.

Figure 5.1 Multiplexer and De-multiplexer

The output value of a 8x1 multiplexer can be represented using the equation (5.1)

$Y = S_2 S_1 S_0 I_o + S_2 S_1 S_0 I_1 + S_2 S_1 S_0 I_2 + S_2 S_1 S_0 I_3 + S_2 S_1 S_0 I_4 + S_2 S_1 S_0 I_5 + S_2 S_1 S_0 I_6 + S_2 S_1 S_0 I_7$

... (5.1)

# <u>PROCEDURE</u>

- 1. Create a module with required number of variables and mention it's input/output.

- 2. Write the description of the multiplexer or demultiplexer using data flow model or gate level model

- 3. Create another module referred as test bench to verify the functionality.

- 4. Follow the steps required to simulate the design and compare the obtained output with the corresponding truth table.

# <u>CODE</u>

$\label{eq:selection} $$ // 8:1 multiplexer module $$ p5(s,i,y); $$ input [7:0]i; $$ input [2:0]s; $$ output y; wire $$ [2:0]sb; $$ not(sb[0],s[0]); $$ not(sb[0],s[0]); $$ not(sb[1],s[1]); $$ not(sb[1],s[1]); $$ not(sb[2],s[2]); $$ assign y = (sb[2]&sb[1]&sb[0]&i[0]) | (sb[2]&sb[1]&sb[0]&i[1]) | $$ (sb[2]&sb[1]&sb[0]&i[2]) | (sb[2]&sb[1]&sb[0]&i[1]) | $$ (sb[2]&sb[1]&sb[0]&i[2]) | (sb[2]&sb[1]&sb[0]&i[3]) | (s[2]&sb[1]&sb[0]&i[4]) | $$ (sb[2]&sb[1]&sb[0]&i[5]) | (s[2]&sb[1]&sb[0]&i[6]) | (s[2]&sb[1]&sb[0]&i[7]); $$ endmodule $$$

## PRE LAB QUESTIONS

DEPT. OF ECE @ MLRITM

- 1. What is a multiplexer?

- 2. What is the relationship between input lines and select lines?

- 3. Why a multiplexer is called a data selector?

- 4. Mention the applications of multiplexer and demultiplexer.

# LAB ASSIGNMENT

5 Implement a full adder with two 4x1 multiplexers.

6 Implement 2 to 4 decoder using 1x4 demultiplexer.

7 Implement a full subtractor with two 4x1 multiplexers.

8 Realize 8x1 mux using 4x1 multiplexer.

- 9 Implement half adder using 2x1 multiplexer.

- 10  $F(W, X, Y, Z) = \prod_{m} (0, 1, 3, 5, 7)$  using 8x1 multiplexer.

- 11 Write code for 1x4 Multiplexer using different coding methods.

# **POST LAB QUESTIONS**

12 Can a multiplexer be used to realize a logic function?

13 Differentiate between decoder and demultiplexer.

14 What are the applications of multiplexers?

15 Design an OR gate from 2:1 MUX.

16 Design a D and T flip flop using 2:1 multiplexer

17Implement the function  $f(A,B,C) = \Sigma m (0,1,3,5,7)$  by using multiplexer.

#### **DESIGN OF CODE CONVERTERS**

EXPT. NO : 06

DATE:

AIM: To Design and simulate the HDL code for the following combinational circuits

4 - Bit binary to gray code converter

4 - Bit gray to binary code converter

Comparator

**RESOURCES**

PC installed with CADENCE tool

## PROGRAM LOGIC

#### Binary to gray code converter logic

This conversion method strongly follows the EX-OR gate operation between binary bits. The steps to perform binary to grey code conversion are given bellow.

> To convert binary to grey code, bring down the most significant digit of the given binary number, because, the first digit or most significant digit of the grey code number is same as the binary number.

> To obtain the successive grey coded bits to produce the equivalent grey coded number for the given binary, add the first bit or the most significant digit of binary to the second one and write down the result next to the first bit of grey code, add the second binary bit to third one and write down the result next to the second bit of grey code, follow this operation until the last binary bit and write down the results based on EX-OR logic to produce the equivalent grey coded binary.

#### Gray to binary code converter logic

This conversion method also follows the EX-OR gate operation between grey & binary bits. The steps to perform grey code to binary conversion are given below.

To convert grey code to binary, bring down the most significant digit of the given grey code number, because, the first digit or the most significant digit of the grey code number is same as the binary number.

To obtain the successive second binary bit, perform the EX-OR operation between the first bit or most significant digit of binary to the second bit of the given grey code.

To obtain the successive third binary bit, perform the EX-OR operation between the second bit or most significant digit of binary to the third MSD (most significant digit) of grey code and so on for the next successive binary bits conversion to find the equivalent.

#### <u>PROCEDURE</u>

Create a module with required number of variables and mention it's input/output.

Write the description of the code converter using data flow model or gate level model.

Create another module referred as test bench to verify the functionality.

Follow the steps required to simulate the design and compare the obtained output with the required one.

#### <u>CODE</u>

// binary to gray code converter module

p7(b,g);

input [3:0] b;

output [3:0] g;

reg [3:0] g;

always@(b)

begin g[3]=b[3];

g[2]=b[3]^b[2];

g[1]=b[2]^b[1];

DEPT. OF ECE @ MLRITM

$g[0]=b[1]^b[0];$ end endmodule //gray to binary converter module p8(g,b); input [3:0] g; output [3:0] b; reg [3:0] b; always@(g) begin b[3]=g[3]; b[2]=b[3]^g[2]; b[1]=b[2]^g[1]; b[0]=b[1]^g[0]; end endmodule

// 4 bit comparator

module p9(a,b,g,l,e); input [3:0]a; input [3:0]b; output g,l,e; reg g,l,e; always@(a,b) begin if (a<b) begin e = 0; 1 = 1; g = 0;end else if (a==b) begin e = 1; 1 = 0; g = 0;end else begin e = 0; 1 = 0; g = 1;end end endmodule

# PRE LAB QUESTIONS

- 1 What is a code converter? List some of the code converters.

- 2 What are the typical applications of gray code?

- 3 Distinguish between the weighted and non-weighted codes. Give examples.

- 4 Realize the Boolean expressions for binary to gray code conversion

- 5 Realize the Boolean expressions for gray to binary code conversion

# LAB ASSIGNMENT

- 1 Design BCD to Excess-3 code converter.

- 2 Design a BCD to seven segment code converter.

- 3 Design octal to binary code converter.

## POST LAB QUESTIONS

- 1. What is the difference between blocking and non-blocking assignments?

- 2. What is the difference between case x and case statements?

- **3.** What is this `timescale compiler directive?

- **4.** What is sensitivity list?

EXPT. NO : 07

DATE:

**AIM:**To write HDL codes for an 8X1 multiplexer and 1X8 demultiplexer and verify its functionality.

# **RESOURCES**

PC installed with CADENCE tool

# PROGRAM LOGIC

In the large-scale-digital systems, a single line is required to carry on two or more digital signals – and, of course! At a time, one signal can be placed on the one line. But, what is required is a device that will allow us to select; and, the signal we wish to place on a common line, such a circuit is referred to as multiplexer.

The function of a multiplexer is to select the input of any 'n' input lines and feed that to one output line. The function of a de-multiplexer is to inverse the function of the multiplexer and the shortcut forms of the multiplexer. The de-multiplexers are mux and demux. Some multiplexers perform both multiplexing and de-multiplexing operations. The main function of the multiplexer is that it combines input signals, allows data compression, and shares a single transmission channel.

Figure 7.1 Multiplexer and De-multiplexer

The output value of a 8x1 multiplexer can be represented using the equation (7.1)

# $Y = S_2 S_1 S_0 I_0 + S_2 S_1 S_0 I_1 + S_2 S_1 S_0 I_2 + S_2 S_1 S_0 I_3 + S_2 S_1 S_0 I_4 + S_2 S_1 S_0 I_5 + S_2 S_1 S_0 I_6 + S_2 S_1 S_0 I_7$ ... (7.1)

For the combination of selection input, the data line is connected to the output line. The 8x1 multiplexer requires 8 AND gates, one OR gate and 3 selection lines. As an input, the combination of selection inputs are giving to the AND gate with the corresponding input data lines.

In a similar fashion, all the AND gates are given connection. In this 8x1 multiplexer, for any selection line input, one AND gate gives a value of 1 and the remaining all AND gates give 0. And, finally, by using OR gate, all the AND gates are added; and, this will be equal to the selected value.

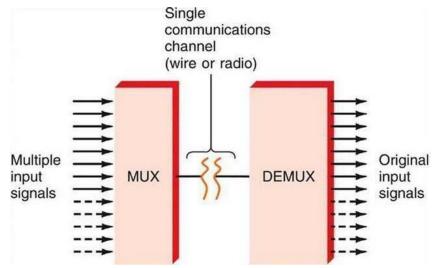

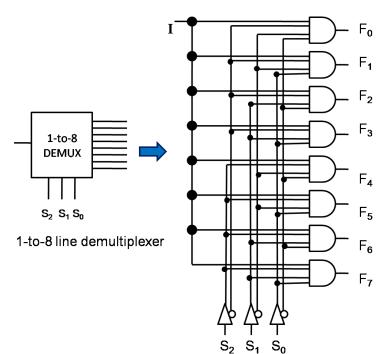

The demultiplexer is also called as data distributors as it requires one input, 3 selected lines and 8 outputs. De-multiplexer takes one single input data line, and then switches it to any one of the output line. 1-to-8 demultiplexer circuit diagram is shown below; it uses 8 AND gates for achieving the operation. The input bit is considered as data D and it is transmitted to the output lines.

Figure 7.2 Demultiplexer circuit diagram

#### <u>PROCEDURE</u>

Create a module with required number of variables and mention it's input/output. Write the description of the multiplexer or demultiplexer using data

32

flow model or gate level model

$Create another module \ referred \ as \ test \ bench \ to \ verify \ the \ functionality.$

Follow the steps required to simulate the design and compare the

obtained output with the corresponding truth table.

#### <u>CODE</u>

|                       | // 8:1      |               |      |

|-----------------------|-------------|---------------|------|

|                       | multiplexer |               |      |

|                       | module      |               |      |

|                       | p5(s,i,y);  |               |      |

|                       |             | input [7:0]i; |      |

|                       | i           |               |      |

|                       | n           |               |      |

|                       | р           |               |      |

|                       | u           |               |      |

|                       | t           |               |      |

| DEPT. OF ECE @ MLRITM |             |               | Page |

```

[

2

:

0

]

S

;

0

u

t

р

u

t

у

;

W

i

r

e

[

2

:

0

]

S

b

;

not(sb[0],s[0]);

not(sb[1],s[1]);

not(sb[2],s[2]);

assign y = (sb[2]\&sb[1]\&sb[0]\&i[0]) | (sb[2]\&sb[1]\&s[0]\&i[1]) |

(sb[2]\&s[1]\&sb[0]\&i[2]) \,|\, (sb[2]\&s[1]\&s[0]\&i[3]) \,|\,

(s[2]&sb[1]&sb[0]&i[4]) |(s[2]&sb[1]&s[0]&i[5]) |

(s[2]\&s[1]\&sb[0]\&i[6]) | (s[2]\&s[1]\&s[0]\&i[7]); endmodule

```

#### //1:8 Demultiplexer

module p6(din,s,do ut); output [7:0]dout; input din ; input [2:0]s; assign dout[7] = din & (s[2]) & (s[1]) & (s[0]); assign dout[6] = din & (s[2]) & (s[1]) & (~s[0]); assign dout[5] = din & (s[2]) & (~s[1]) & (~s[0]); assign dout[4] = din & (s[2]) & (~s[1]) & (s[0]); assign dout[3] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[2] = din & (~s[2]) & (s[1]) & (s[0]); assign dout[1] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]); assign dout[0] = din & (~s[2]) & (~s[1]) & (s[0]);

#### PRE LAB QUESTIONS

- 1. What is a multiplexer?

- 2. What is the relationship between input lines and select lines?

- 3. Why a multiplexer is called a data selector?

- 4. Mention the applications of multiplexer and demultiplexer.

#### <u>LAB ASSIGNMENT</u>

- 1. Implement a full adder with two 4x1 multiplexers.

- 2. Implement 2 to 4 decoder using 1x4 demultiplexer.

- 3. Implement a full subtractor with two 4x1 multiplexers.

- 4. Realize 8x1 mux using 4x1 multiplexer.

- 5. Implement half adder using 2x1 multiplexer.

- 6.  $F(W, X, Y, Z) = \prod_{m} (0, 1, 3, 5, 7)$  using 8x1 multiplexer.

7. Write code for 1x4 Multiplexer using different coding methods.

## POST LAB QUESTIONS

- 1. Can a multiplexer be used to realize a logic function?

- 2. Differentiate between decoder and demultiplexer.

- 3. What are the applications of multiplexers?

- 4. Design an OR gate from 2:1 MUX.

- 5. Design a D and T flip flop using 2:1 multiplexer

- 6. Implement the function  $f(A,B,C) = \Sigma m (0,1,3,5,7)$  by using multiplexer.

| Modelling of an Edge triggered and Level triggered FFs : D, SR, | EXPT. NO : 08 |

|-----------------------------------------------------------------|---------------|

| JK                                                              | DATE:         |

AIM: To write HDL codes for SR, JK, D, T flip flops and verify its functionality.

#### **RESOURCES**

PC installed with Xilinx tool

#### PROGRAM LOGIC

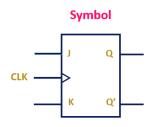

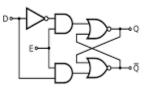

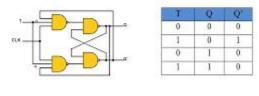

Each flip-flop stores a single bit of data, which is emitted through the Q output on the output section side. Normally, the value can be controlled via the inputs to the input side. In particular, the value changes when the clock input, marked by a triangle on each flip-flop, rises from 0 to 1 (or otherwise as configured); on this rising edge, the value changes according to the tables below.

#### Table 7.1 Truth tables of D, T, SR, JK flip flops

## J K Flip Flop

| Truth Table |   |   |              |  |  |

|-------------|---|---|--------------|--|--|

| CLK         | J | K | <b>Q</b> n+1 |  |  |

| 1           | 0 | 0 | <b>Q</b> n   |  |  |

| ↑           | 0 | 1 | 0            |  |  |

| ↑           | 1 | 0 | 1            |  |  |

| 1           | 1 | 1 | Q n'         |  |  |

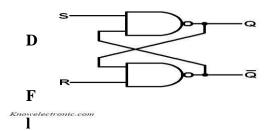

#### **S R Flip Flop**

SR Flip Flop

| Sno | S | R | Q | Q' | State          |

|-----|---|---|---|----|----------------|

| 1   | 1 | 0 | 1 | 0  | Q is set to 1  |

| 2   | 1 | 1 | 1 | 0  | No change      |

| 3   | 0 | 1 | 0 | 1  | Q' is set to 1 |

| 4   | 1 | 1 | 0 | 1  | No change      |

| 5   | 0 | 0 | 1 | 1  | Invalid        |

#### ip Flop.

# D Flip Flop Circuit

| D                           | s | R | Q                 | State     |

|-----------------------------|---|---|-------------------|-----------|

|                             | 0 | 0 | Previous<br>State | No Change |

| 0                           | 0 | 1 | 0                 | Reset     |

| 1                           | 1 | 0 | 1                 | Set       |

|                             | 1 | 1 | ?                 | Forbidden |

| SR & D Flip Flop TruthTable |   |   |                   |           |

#### **T Flip Flop**

#### T Flip Flop Circuit 74HC74

CORCUTE DIV

Another way of describing the different behavior of the flip-flops is in English text.

**D** Flip-Flop: When the clock triggers, the value remembered by the flip-flop becomes the value of the D input (Data) at that instant.

**T Flip-**Flop: When the clock triggers, the value remembered by the flip-flop either toggles or remains the same depending on whether the T input (Toggle) is 1 or 0.

**J-K Flip-Flo**p: When the clock triggers, the value remembered by the flip-flop toggles if the J and K inputs are both 1, remains the same if they are both 0; if they are different, then the value becomes 1 if the J (Jump) input is 1 and 0 if the K (Kill) input is 1.

**S-R Flip-Flop:** When the clock triggers, the value remembered by the flip-flop remains unchanged if R and S are both 0, becomes 0 if the R input (Reset) is 1, and becomes 1 if the S input (Set) is 1. The behavior in unspecified if both inputs are 1.

#### <u>PROCEDURE</u>

- Create a module with required number of variables and mention it's input/output.

- Write the description of the flip flops using behavioral model

- Create another module referred as test bench to verify the functionality.

- Follow the steps required to simulate the design and compare the obtained output with the required one.

# <u>CODE</u>

#### //SR flipflop

```

module p14(s,r,clk,q,qb);

input s,r,clk;

output q,qb; reg

q,qb; reg [1:0]sr;

wire qp=1'b0;

always@(posedge clk) begin

sr = \{s,r\};

begin case

(sr)

2'd0:q=qp;

2'd1:q=1'b0;

2'd2:q=1'b1;

2'd3:q=1'bX;

endcase end

qb=~q; end

endmodule

```

#### //JK flipflop

```

module p15(j,k,clk,q,qb);

input j,k,clk;

output q,qb; reg

q,qb; reg [1:0]jk;

wire qp=1'b0;

always@(posedge clk) begin

DEPT. OF ECE @ MLRITM

```

jk={j,k}; begin case (jk) 2'd0:q=qp; 2'd1:q=1'b0; 2'd2:q=1'b1;

2'd3:q=~q; endcase end qb=~q; end endmodule

#### //D flipflop

```

module p16(q,din,clk);

output q;

reg q; input din

; wire din ;

input clk ;

always @ (posedge (clk))

begin q = din ;

end endmodule

```

## //T flipflop

```

module p17(q,t,clk);

output q;

reg q; input t;

input clk ;

always @ (posedge (clk))

begin

q = ~t; end

endmodule

```

#### PRE LAB QUESTIONS

DEPT. OF ECE @ MLRITM

1 Distinguish between latch and edge triggered flip-flop?

2 What is the cause for the race around phenomenon in a J - K flip-flop?

3 What is meant by triggering of a flip-flop?

4 What do you mean by clock skew?

5 What is master-slave flip-flop?

#### LAB ASSIGNMENT

6 Convert a given J-K flip-flop in to a D flip-flop using additional logic if necessary?

7 Convert a given J-K flip-flop in to a T flip-flop using additional logic if necessary?

8 Convert a given D flip-flop in to a T flip-flop using additional logic if necessary?

9 Implement an asynchronous reset JK FF.

#### POST LAB QUESTIONS

10 What is use of characteristic and excitation table?

11 How is a JK flip flop made to toggle?

12 Differentiate between combinational and sequential circuits.

#### Design of 4-bit binary, BCD counters (synchronous/

asynchronous reset) or any

#### sequence counter

EXPT. NO: 9

DATE:

#### AIM: To write HDL codes for the following counters.

Binary counter

BCD counter (Synchronous reset and asynchronous reset)

# **RESOURCES**

PC installed with CAEDENCE tool

# PROGRAM LOGIC

Counter is a sequential circuit. A digital circuit which is used for counting pulses is known as counter. Counter is the widest application of flip-flops. It is a group of flip- flops with a clock signal applied. Counters are of two types.

Asynchronous or ripple counters.

Synchronous counters.

Asynchronous counters are called as ripple counters, the first flip-flop is clocked by the external clock pulse and then each successive flip-flop is clocked by the output of the preceding flip-flop. The term asynchronous refers to events that do not have a fixed time relationship with each other. An asynchronous counter is one in which the flip-flops within the counter do not change states at exactly the same time because they do not have a common clock pulse

In synchronous counters, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses. Thus, all the flip-flops change state simultaneously (in parallel).

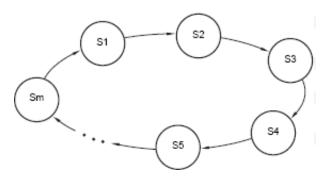

A counter is a register capable of counting the number of clock pulses arriving at its clock input. Count represents the number clock pulses arrived. A specified sequence of states appears as the counter output. The name counter is generally used for clocked sequential circuit whose state diagram contains a single cycle. The modulus of a counter is the number of states in the cycle. A counter with m states is called a modulo-m counter or divide-by-m counter. A counter with a non-power-of-2 modulus has extra states that are not used in normal DEPT. OF ECE @ MLRITM Page 41

operation. There are two types of counters, synchronous and asynchronous. In synchronous counter, the common clock is connected to all the flip-flops and thus they are clocked simultaneously.

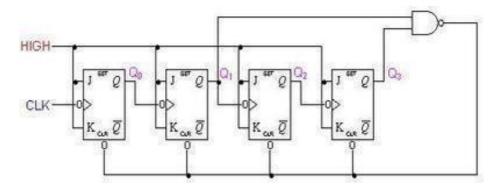

Fig. 9.1 General structure of a counter's state diagram – a single cycle

#### Asynchronous Decade Counters

The *modulus* is the number of unique states through which the counter will sequence. The maximum possible number of states of a counter is  $2^n$ where n is the number of flip-flops. Counters can be designed to have a number of states in their sequence that is less than the maximum of  $2^n$ . This type of sequence is called a truncated sequence. One common modulus for counters with truncated sequences is 10 (Modules10). A decade counter with a count sequence of zero (0000) through 9 (1001) is a BCD decade counter because its 10-state sequence produces the BCD code. To obtain a truncated sequence, it is necessary to force the counter to recycle before going through all of its possible states. A decade counter requires 4flip-flops. One way to make the counter recycle after the count of 9 (1001) is to decode count 10 (1010) with a NAND gate and connect the output of the NAND gate to the clear (CLR) inputs of the flip-flops, as shown in Figure 9.1

Figure 9.2 Asynchronous Decade Counter

#### Synchronous Decade Counters

Figure 9.3 Asynchronous Decade Counter

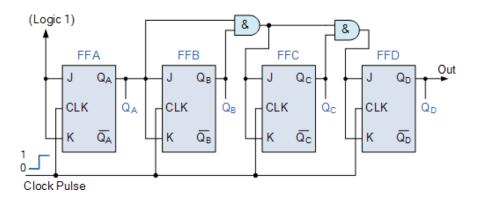

It can be seen from Figure 8.2, that the external clock pulses (pulses to be counted) are fed directly to each of the J-K flip-flops in the counter chain and that both the J and K inputs are all tied together in toggle mode, but only in the first flip-flop, flip- flop FFA (LSB) are they connected HIGH, logic "1" allowing the flip-flop to toggle on every clock pulse. Then the synchronous counter follows a predetermined sequence of states in response to the common clock signal, advancing one state for each pulse.

The J and K inputs of flip-flop FFB are connected directly to the output QA of flip- flop FFA, but the J and K inputs of flip-flops FFC and FFD are driven from separate AND gates which are also supplied with signals from the input and output of the previous stage. These additional AND gates generate the required logic for the JK inputs of the next stage.

If we enable each JK flip-flop to toggle based on whether or not all preceding flip- flop outputs (Q) are "HIGH" we can obtain the same counting sequence as with the asynchronous circuit but without the ripple effect, since each flip-flop in this circuit will be clocked at exactly the same time.

## <u>PROCEDURE</u>

- **1.** Create a module with required number of variables and mention it's input/output.

- **2.** Write the description of the counter to count required number of states and to satisfy its conditions.

- **3.** Create another module referred as test bench to verify the functionality.

- **4.** Follow the steps required to simulate the design and compare the obtained output with the required one.

# <u>CODE</u>

// binary counter module p18(clk,count ); output [3:0] count ; reg [3:0] count ; input clk; wire clk : initial count = 0; always @ (posedge (clk)) begin  $count \le count + 1; end$ endmodule //BCD counter module p19(clk, reset, dout); output [3:0] dout ; reg [3:0] dout ; input clk; wire clk ; input reset; wire reset; initial dout = 0; always @ (posedge (clk)) begin if (reset) dout <= 0; else if (dout<=9) begin dout  $\leq$  dout + 1; end else if (dout==9) begin dout  $\leq 0$ ; end end endmodule

## PRE LAB QUESTIONS

- 1. How many number of flip-flops required in a decade counter?

- 2. How many number of flip-flops required in a Mod N Counter?

- 3. What is the difference between synchronous and asynchronous counters?

- 4. An n stage ripple counter can count up to\_\_\_\_\_.

## LAB ASSIGNMENT

Design and implement a synchronous 3 – bit up/down counter using J-K flip- flops. Implement a ring counter. Implement a Johnson counter. Design a 4-bit ripple counter and verify its functionality.

#### POST LAB QUESTIONS

What is an asynchronous counter?

How is it different from a synchronous counter?

What are the advantages of synchronous counters?